# Samsung e·MMC Product family

## e.MMC 4.41 Specification compatibility

# datasheet

SAMSUNG ELECTRONICS RESERVES THE RIGHT TO CHANGE PRODUCTS, INFORMATION AND SPECIFICATIONS WITHOUT NOTICE.

Products and specifications discussed herein are for reference purposes only. All information discussed herein is provided on an "AS IS" basis, without warranties of any kind.

This document and all information discussed herein remain the sole and exclusive property of Samsung Electronics. No license of any patent, copyright, mask work, trademark or any other intellectual property right is granted by one party to the other party under this document, by implication, estoppel or otherwise.

Samsung products are not intended for use in life support, critical care, medical, safety equipment, or similar applications where product failure could result in loss of life or personal or physical harm, or any military or defense application, or any governmental procurement to which special terms or provisions may apply.

For updates or additional information about Samsung products, contact your nearest Samsung office.

All brand names, trademarks and registered trademarks belong to their respective owners.

2011 Samsung Electronics Co., Ltd. All rights reserved.

## Revision History

| Revision No. | History                                                                                                                                                                                                                                       | Draft Date    | <u>Remark</u> | Editor  |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------|

| 0.0          | 1. Initial issue                                                                                                                                                                                                                              | Sep. 28, 2011 | Target        | S.M.Lee |

| 1.0          | <ol> <li>Initialization time is deleted in Table 22</li> <li>Performance is updated with measured value in Chapter 5.2.3</li> <li>SEC_TRIM_MULT is chagend to 0x11 in Chapter 6.4</li> <li>Write Timeout is updated in Chapter 7.1</li> </ol> | Nov. 16, 2011 | Final         | S.M.Lee |

| 1.1          | 1. Max. Enhanced Partition Size of 16GB is changed in Table 25<br>2. MAX_ENH_SIZE_MULT of 16GB is changed to 0xBA in Chapter 6.4                                                                                                              | Dec. 12, 2011 | Final         | S.M.Lee |

## Revision History Appendix(1.0)

| Before(ver.0.0)                                                                                                     |                                                                                                     |                             |            | After(ver.1.0)                         |                                 |            |                                      |                                                                                                                                 |                                                                                                                      |                          |                 |                                        |                       |           |                                 |

|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------|------------|----------------------------------------|---------------------------------|------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--------------------------|-----------------|----------------------------------------|-----------------------|-----------|---------------------------------|

| Table 32] Perfo                                                                                                     | rmance                                                                                              |                             |            |                                        |                                 |            |                                      | [Table 32] Performa                                                                                                             | nce                                                                                                                  |                          |                 |                                        |                       |           |                                 |

| Density                                                                                                             | Se                                                                                                  | equential Read (MB          | /s)        | s) Sequential Write (MB/s)             |                                 |            | Density Sequential Read (MB/s)       |                                                                                                                                 | ) Sequential                                                                                                         |                          | ntial Write     | Write (MB/s)                           |                       |           |                                 |

| 16 GB                                                                                                               |                                                                                                     |                             |            |                                        |                                 |            |                                      | 16 GB                                                                                                                           |                                                                                                                      |                          |                 |                                        |                       |           |                                 |

| 32 GB                                                                                                               | 1                                                                                                   | 80                          |            |                                        |                                 | 35         |                                      | 32 GB                                                                                                                           |                                                                                                                      | 80                       |                 |                                        |                       | 35        |                                 |

| 64 GB                                                                                                               |                                                                                                     |                             |            |                                        |                                 |            |                                      | 64 GB                                                                                                                           |                                                                                                                      |                          |                 |                                        |                       |           |                                 |

| Tes∜ Estimatio                                                                                                      | on Conditio                                                                                         | n : Bus width x8, 52N       | IHz DDR, 4 | MB da                                  | ta transfer, w                  | /o file sy | stem overhead                        | * Test Condition : Bu                                                                                                           | us width x8, 5                                                                                                       | 2MHz DDR, 4MB File Trans | sfer, measure   | ed on Sar                              | nsung's Internal      | Board, w/ | o file system                   |

| Table 37] Exte                                                                                                      | ended CSD                                                                                           | Register                    |            |                                        |                                 |            |                                      | [Table 37] Exte                                                                                                                 | ended CSE                                                                                                            | Register                 |                 |                                        |                       |           |                                 |

| Nam                                                                                                                 | e                                                                                                   | Field                       |            | Cell<br>Type                           | CSD-slice                       |            | SD Value<br>32GB 64GB                | Name                                                                                                                            | •                                                                                                                    | Field                    | Size<br>(Bytes) | Cell<br>Type                           | CSD-slice             |           | CSD Value<br>3 32GB             |

| Secure TRIM                                                                                                         | Multiplier                                                                                          | SEC_TRIM_MULT               | 1          | R                                      | [229]                           |            | 0x1B                                 | Secure TRIM                                                                                                                     | Multiplier                                                                                                           | SEC_TRIM_MULT            | 1               | R                                      | [229]                 |           | 0x11                            |

| 7.1 Time                                                                                                            | Param                                                                                               | eter                        |            |                                        |                                 | +:         |                                      | 7.1 Time                                                                                                                        |                                                                                                                      |                          |                 |                                        |                       |           |                                 |

| 7.1 Time                                                                                                            | Param<br>iming Par                                                                                  |                             |            | Max. '                                 | Value                           | + - :      | Unit                                 | [Table 38] Tir                                                                                                                  | me Parar                                                                                                             | neter                    |                 |                                        |                       |           |                                 |

| 7.1 Time                                                                                                            | iming Par                                                                                           | ramter                      |            | Max. 1                                 |                                 | + :        | Unit<br>s                            | [Table 38] Tir<br>Ti                                                                                                            | me Parar<br>ming Pa                                                                                                  | neter<br>r <b>amter</b>  |                 | Max.                                   |                       |           | Unit                            |

| 7.1 Time<br>Ti                                                                                                      | <b>iming Pa</b><br>Time (tIN                                                                        | ramter                      |            |                                        | 1                               |            |                                      | [Table 38] Tir<br>Ti<br>Initialization                                                                                          | me Parar<br><b>ming Pa</b><br>Time (til                                                                              | neter<br>r <b>amter</b>  |                 | 1                                      |                       |           | S                               |

| 7.1 Time<br>Ti<br>Initialization                                                                                    | <mark>iming Par</mark><br>Time (tIN<br>out                                                          | ramter                      |            | 1                                      | 0                               |            | S                                    | [Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo                                                                            | me Parar<br>ming Pa<br>Time (til<br>out                                                                              | neter<br>r <b>amter</b>  |                 | 1                                      | 0                     |           | s<br>ms                         |

| 7.1 Time<br>Ti<br>Initialization<br>Read Timeo                                                                      | <mark>iming Par</mark><br>Time (tIN<br>out<br>ut                                                    | ramter                      |            | 1                                      | I<br>)0<br>TBD)                 |            | s<br>ms                              | [Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo                                                             | me Parar<br>ming Pa<br>Time (til<br>put<br>put                                                                       | neter<br>r <b>amter</b>  |                 | 1<br>10<br>35                          | 0                     |           | s<br>ms<br>ms                   |

| 7.1 Time<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo                                                       | <b>iming Par</b><br>Time (tIN<br>out<br>ut<br>out                                                   | ramter                      |            | 1<br>10<br>300 (1<br>1                 | I<br>)0<br>TBD)                 |            | s<br>ms<br>ms                        | Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo                                               | me Parar<br>ming Pa<br>Time (tll<br>out<br>out<br>out                                                                | nete r<br>ramter         |                 | 1<br>10<br>35<br>1                     | 00<br>50<br>5         |           | s<br>ms<br>ms<br>ms             |

| 7.1 Time<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo                                        | iming Par<br>Time (tIN<br>out<br>out<br>out<br>Time out                                             | ramter<br>IT)               |            | 1<br>10<br>300 (1<br>1                 | 1<br>00<br>TBD)<br>5<br>3       |            | s<br>ms<br>ms<br>ms                  | Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase                                | me Parar<br>ming Pa<br>Time (til<br>out<br>out<br>out<br>out<br>e Time ou                                            | nete r<br>ramter<br>VIT) |                 | 1<br>10<br>35<br>1<br>3                | 00<br>50<br>5         |           | s<br>ms<br>ms<br>ms<br>min      |

| 7.1 Time<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase                         | iming Par<br>Time (tIN<br>out<br>ut<br>out<br>e Time out<br>se Time ou                              | ramter<br>IT)<br>t          |            | 1<br>10<br>300 (1<br>1!<br>3           | 1<br>00<br>TBD)<br>5<br>3       |            | s<br>ms<br>ms<br>ms<br>min           | Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase<br>Secure Erase                | me Parar<br>ming Pa<br>Time (tll<br>out<br>out<br>out<br>e Time ou<br>se Time ou                                     | neter<br>ramter<br>NIT)  |                 | 1<br>10<br>35<br>1<br>3<br>8           | 5<br>3<br>3           |           | s<br>ms<br>ms<br>ms<br>min<br>s |

| 7.1 Time<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase<br>Secure Eras          | iming Par<br>Time (tIN<br>out<br>ut<br>out<br>Time out<br>se Time out<br>se Time out<br>n step1 Tim | ramter<br>IT)<br>t<br>neout |            | 1<br>10<br>300 (`<br>1!<br>3<br>8<br>5 | 1<br>00<br>TBD)<br>5<br>3       |            | s<br>ms<br>ms<br>ms<br>min<br>s      | Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase<br>Secure Erase<br>Secure Trim | me Parar<br>ming Pa<br>Time (til<br>out<br>out<br>e Time ou<br>se Time ou<br>se Time o<br>n step 1 Ti                | neter<br>ramter<br>NIT)  |                 | 1<br>10<br>35<br>1<br>3                | 5<br>3<br>3           |           | s<br>ms<br>ms<br>min<br>s<br>s  |

| 7.1 Time<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase<br>Secure Eras<br>Secure Trim | iming Par<br>Time (tIN<br>out<br>out<br>e Time out<br>se Time out<br>s step1 Tin<br>n step2 Tin     | ramter<br>IT)<br>t<br>neout |            | 1<br>10<br>300 (`<br>1!<br>3<br>8<br>5 | 5<br>5<br>3<br>3<br>5<br>3<br>3 |            | s<br>ms<br>ms<br>ms<br>min<br>s<br>s | Table 38] Tir<br>Ti<br>Initialization<br>Read Timeo<br>Write Timeo<br>Erase Timeo<br>Force Erase<br>Secure Erase                | me Parar<br>ming Pa<br>Time (til<br>out<br>out<br>e Time ou<br>se Time ou<br>se Time ou<br>n step1 T<br>n step2 Time | neter<br>ramter<br>NIT)  |                 | 1<br>10<br>35<br>1<br>3<br>8<br>8<br>5 | 5<br>3<br>3<br>3<br>3 |           | s<br>ms<br>ms<br>ms<br>min<br>s |

## Revision History Appendix(1.1)

|                                 | Before(ver.1.0)                    |                |             |          |                                                                                        |                | After(ver.1.1)                                                                               |                     |         |

|---------------------------------|------------------------------------|----------------|-------------|----------|----------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------|---------------------|---------|

| [Table 38]                      | Time Parameter                     |                |             |          | [Table 38] Time Par                                                                    | rameter        |                                                                                              |                     |         |

| Timing Paramter Max. Value Unit |                                    |                |             | Timing F | Paramter                                                                               | Max. Value     | Unit                                                                                         |                     |         |

| Initializatio                   | on Time (tINIT)                    | 1              | S           |          | Initialization Time (                                                                  | (HNIT)         | Normal 1)                                                                                    | 1                   | S       |

| Read Tim                        | eout                               | 100            | ms          |          | ninaan2aaron ninnen                                                                    | (              | After partition setting <sup>2)</sup>                                                        | 3                   | S       |

| Write Time                      | eout                               | 350            | ms          |          | Read Timeout                                                                           |                |                                                                                              | 100                 | ms      |

| Erase Tim                       |                                    | 15             | ms          |          | Write Timeout                                                                          |                |                                                                                              | 350                 | ms      |

|                                 |                                    |                |             |          | Erase Timeout                                                                          |                |                                                                                              | 15                  | ms      |

| Force Era                       | se Timeout                         | 3              | min         |          | Force Erase Time                                                                       | out            |                                                                                              | 3                   | min     |

| Secure Er                       | rase Timeout                       | 8              | S           |          | Secure Erase Time                                                                      | eout           |                                                                                              | 8                   | S       |

| Secure Tr                       | im step1 Timeout                   | 5              | S           |          | Secure Trim step1                                                                      | Timeout        |                                                                                              | 5                   | S       |

| Secure Tr                       | im step2 Timeout                   | 3              | S           |          | Secure Trim step2                                                                      | Timeout        |                                                                                              | 3                   | S       |

| Trim Time                       | out <sup>1)</sup>                  | 600            | ms          |          | Trim Timeout 3)                                                                        |                |                                                                                              | 600                 | ms      |

|                                 | Switching Timeout (after Init)     | 100            |             |          | Partition Switching                                                                    | ) Timeout (a   | ifier Init)                                                                                  | 100                 | us      |

| NOTE:                           | ze and Address are aligned, Max. T |                | US<br>300ms |          | NOTE:<br>1) Normal Initialization<br>2) Initialization Time a<br>3) If 8KB Size and Ad | fter partition | it partition setting<br>setting, refer to INI_TIMEOUT_AP<br>gned, Max. Timeout value is 300m | in 6.4 EXT_CSD<br>s | registe |

| e 25] Maxi                      | mum Enhanced Partition Size        |                |             | į        | [Table 25] Maxim                                                                       | um Enhai       | nced Partition Size                                                                          |                     |         |

| Device                          | Max. Enhanced F                    | Partition Size |             |          | Device                                                                                 |                | Max. Enhanced Partition                                                                      | on Size             |         |

| 16 GB                           | 7,759,462,40                       | 0 Bytes        |             | 71       | 16 GB                                                                                  |                | 7,801,405,440 Byte                                                                           | es                  |         |

|                                 |                                    |                |             | ─┤ ŀ     | I                                                                                      |                |                                                                                              |                     |         |

## Table Of Contents

| 2.0 KEY FEATURES.       4         3.0 PACKAGE CONFIGURATIONS       5         3.119 Bill Pin Configuration       5         3.111 12mm x 16mm x 1.1mm Package Dimension       6         3.12 12mm x 16mm x 1.1mm Package Dimension       7         3.2 Product Architecture       8         4.0 e MMC 4.41 features       9         4.1 Data Write       9         4.2 Reliable Write       10         4.3 Secure Trim       10         4.4 Reliable Write       10         4.3 Secure Trim       10         4.4 Sequer Trim       10         4.5 Background Operation       12         5.0 Technical Notes       13         5.1.1 Partition Management       13         5.1.1 Derive a Write Protection       14         5.1.2 User Area Write Protection       14         5.1.2 User Area Write Protection       14         5.1.3 Boot operation       16         5.1.4 Wear Leveling       16         5.1.5 User Area Write Protection       17         5.1.6 Auto Power Saying Mode       17         5.1.7 Liver Area Write Protection       16         5.1.8 Doot operation       16         5.1.9 Coot Partition Write Protection       16                                       | 1.0 PRODUCT LIST                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 3.1 169 Bail Pin Configuration       5         3.1.1 21mm × 16mm × 1.1mm Package Dimension       7         3.2 Product Architecture       8         4.0 e.MMC 4.41 features       9         4.1 Data Write       9         4.2 Reliable Write       9         4.2 Reliable Write       9         4.2 Reliable Write       10         4.3 Secure Trim       10         4.4 High Priority Interrupt.       10         4.5 Background Operation       12         5.0 Technical Notes       13         5.1.1 Partition Management       13         5.1.1.1 Boot Area Partition and RPMB Area Partition       13         5.1.1.2 Enhanced Partition Arceal       14         5.1.2 Enhanced Partition Arceal       14         5.1.3 Eoot area trivite Protection       14         5.1.4 Doot operation       14         5.1.5 User Density       16         5.1.6 Write Protection       14         5.1.7 End of Life Management       17         5.1.8 Ware Levering       16         5.1.4 Were Levering       17         5.1.5 User Density       16         5.1.6 Ware Levering       17         5.1.7 End of Life Management       17         5.1.                                    | 2.0 KEY FEATURES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4                                                                                                                                            |

| 4.1 Deta Write       9         4.2 Reliable Write       10         4.3 Secure Trim       10         4.4 High Priority Interrupt       10         4.5 Background Operation       12         5.0 Technical Notes       13         5.1 1 Partition Management       13         5.1.1 Partition Management       13         5.1.1 Enhanced Partition (Area)       13         5.1.1 User Area Write Protection       14         5.1.2 Write protect management       14         5.1.2 User Area Write Protection       14         5.1.2 User Area Write Protection       14         5.1.3 User Area Write Protection       14         5.1.4 User Area Write Protection       14         5.1.5 User Density       16         5.1.4 User Area Write Protection       15         5.1.4 User Density       16         5.1.5 User Density       16         5.1.6 User Density       17         5.2.1 Fand to Life Management       17         5.2.2 Strant Report Output Data (For Customer)       18         5.2.3 Performance       18         6.0 REGISTER VALUE       19         6.1 OCR Register       19         6.2 CID Register       19         6.                                    | <ul> <li>3.1 169 Ball Pin Configuration</li> <li>3.1.1 12mm x 16mm x 1.0mm Package Dimension</li> <li>3.1.2 12mm x 16mm x 1.2mm Package Dimension</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 5<br>6<br>7                                                                                                                                  |

| 5.1 SW Agorithm       13         5.1.1 Partition Management       13         5.1.1 Partition Management       13         5.1.1 Z Enhanced Partition (Area)       13         5.1.2 Live protect management       14         5.1.2 Uiser Area Write Protection       14         5.1.2 Uiser Area Write Protection       14         5.1.3 Boot operation       15         5.1.4 Wear Leveling       16         5.1.5 User Density       16         5.1.6 Auto Power Saving Mode       17         5.1.7 End of Life Management       17         5.2.1 Smart Report Sequence       17         5.2.2 Smart Report Output Data (For Customer)       18         5.2.3 Performance       19         6.1 OCR Register       19         6.2 CID Register       19         6.3 CSD Register       20         6.4 Extended CSD Register       20         7.4 Den-drain mode bus signal level.       27         7.4 Dust data rate operation       26         7.4 Dust data rate interface timings       27         7.4 Dust data rate interface timings       24         7.4 Dust data rate interface timings       27         7.4 Dus data rate interface timings       26         7.4 Push-pull | <ul> <li>4.1 Data Write</li> <li>4.2 Reliable Write</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9<br>10<br>10<br>10<br>12                                                                                                                    |

| 6.1 OCR Register       19         6.2 CID Register       19         6.2 CID Register       19         6.3 CSD Register       20         6.4 Extended CSD Register       20         7.0 AC PARAMETER       24         7.1 Time Parameter       24         7.3 Bus timing for DAT signals during 2x data rate operation       26         7.4 Sus timing for DAT signals during 2x data rate operation       26         7.4 I Open-drain mode bus signal level.       27         7.4.1 Open-drain mode bus signal level.high-voltage MultiMediaCard       27         7.4.2 Push-pull mode bus signal level.high-voltage MultiMediaCard       27         7.4.4 Push-pull mode bus signal level.et MIC       28         8.0 DC PARAMETER       29         8.1 Active Power Consumption during operation       29         8.2 Standby Power Consumption in auto power saving mode and standby state       29         8.3 Sleep Power Consumption in Sleep State       29         8.4 Supply Voltage       29         8.5 Bus Signal Line Load       30         9.0 e-MMC Connection Guide       31         9.1 x8 support Host connection Guide       31                                   | <ul> <li>5.1 S/W Agorithm</li> <li>5.1.1 Partition Management</li> <li>5.1.1 Boot Area Partition and RPMB Area Partition</li> <li>5.1.2 Enhanced Partition (Area)</li> <li>5.1.2 Write protect management</li> <li>5.1.2.1 User Area Write Protection</li> <li>5.1.2.2 Boot Partition Write Protection</li> <li>5.1.2.2 Boot operation</li> <li>5.1.3 Boot operation</li> <li>5.1.4 Wear Leveling</li> <li>5.1.5 User Density</li> <li>5.1.6 Auto Power Saving Mode</li> <li>5.1.7 End of Life Management</li> <li>5.2.1 Smart Report</li> <li>5.2.2 Smart Report Sequence</li> <li>5.2.3 Performance</li> </ul> | 13<br>13<br>13<br>13<br>13<br>14<br>14<br>14<br>14<br>14<br>14<br>15<br>16<br>16<br>16<br>17<br>17<br>17<br>17<br>17<br>17<br>17<br>18<br>18 |

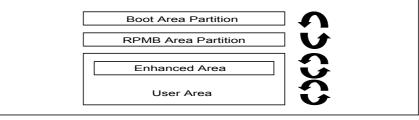

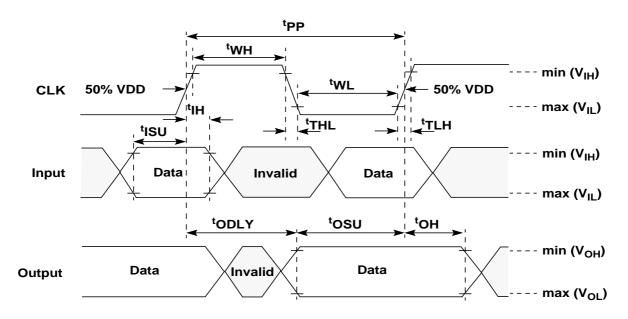

| 7.1 Time Parameter       24         7.2 Bus Timing Parameter       24         7.3 Bus timing for DAT signals during 2x data rate operation       26         7.3.1 Dual data rate interface timings       26         7.4 Bus signal levels       27         7.4.1 Open-drain mode bus signal level       27         7.4.2 Push-pull mode bus signal level.       27         7.4.3 Push-pull mode bus signal level.dual-voltage MultiMediaCard       27         7.4.4 Push-pull mode bus signal level.e <sup>MMC</sup> 28         8.0 DC PARAMETER       29         8.1 Active Power Consumption during operation       29         8.2 Standby Power Consumption in auto power saving mode and standby state       29         8.3 Sleep Power Consumption in Sleep State       29         8.4 Supply Voltage       29         8.5 Bus Operating Conditions       29         8.6 Bus Signal Line Load       30         9.0 e-MMC Connection Guide       31         9.1 x8 support Host connection Guide       31                                                                                                                                                                        | 6.1 OCR Register     6.2 CID Register     6.2.1 Product name table (In CID Register)     6.3 CSD Register                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                              |

| 8.1 Active Power Consumption during operation       29         8.2 Standby Power Consumption in auto power saving mode and standby state       29         8.3 Sleep Power Consumption in Sleep State       29         8.4 Supply Voltage       29         8.5 Bus Operating Conditions       29         8.6 Bus Signal Line Load       30         9.0 e·MMC Connection Guide       31         9.1 x8 support Host connection Guide       31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <ul> <li>7.0 AC PARAMETER.</li> <li>7.1 Time Parameter</li> <li>7.2 Bus Timing Parameter</li> <li>7.3 Bus timing for DAT signals during 2x data rate operation</li> <li>7.3.1 Dual data rate interface timings</li> <li>7.4 Bus signal levels</li> <li>7.4.1 Open-drain mode bus signal level.</li> <li>7.4.2 Push-pull mode bus signal level.high-voltage MultiMediaCard</li> <li>7.4.3 Push-pull mode bus signal level.dual-voltage MultiMediaCard</li> </ul>                                                                                                                                                  | 24<br>24<br>24<br>26<br>26<br>26<br>27<br>27<br>27<br>27<br>27<br>27                                                                         |

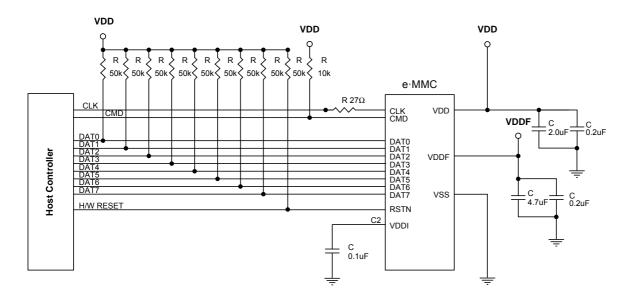

| 9.1 x8 support Host connection Guide                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <ul> <li>8.1 Active Power Consumption during operation</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 31                                                                                                                                           |

## **INTRODUCTION**

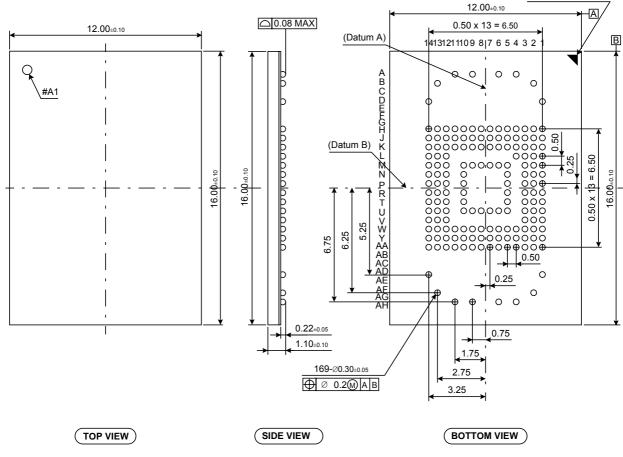

The SAMSUNG e·MMC is an embedded MMC solution designed in a BGA package form. e·MMC operation is identical to a MMC card and therefore is a simple read and write to memory using MMC protocol v4.41 which is a industry standard.

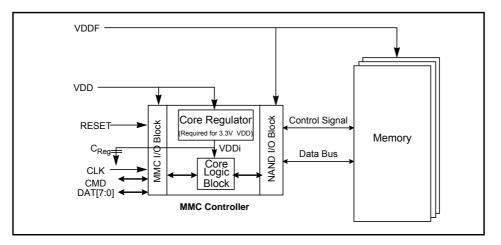

e·MMC consists of NAND flash and a MMC controller. 3V supply voltage is required for the NAND area (VDDF) whereas 1.8V or 3V dual supply voltage (VDD) is supported for the MMC controller. Maximum MMC interface frequency of 52MHz and maximum bus widths of 8 bit are supported.

There are several advantages of using e-MMC. It is easy to use as the MMC interface allows easy integration with any microprocessor with MMC host. Any revision or amendment of NAND is invisible to the host as the embedded MMC controller insulates NAND technology from the host. This leads to faster product development as well as faster times to market.

The embedded flash mangement software or FTL(Flash Transition Layer) of e<sup>.</sup>MMC manages Wear Leveling, Bad Block Management and ECC. The FTL supports all features of the Samsung NAND flash and achieves optimal performance.

## **1.0 PRODUCT LIST**

#### [Table 1] Product List

| Capacities | e-MMC Part ID   | NAND Flash Type | User Density (%) | Power System                           | Package size        | Pin Configuration |

|------------|-----------------|-----------------|------------------|----------------------------------------|---------------------|-------------------|

| 16GB       | KLMAG2GE4A-A001 | 64Gb MLC x 2    |                  | - Interface power : VDD                | 12mm x 16mm x 1.0mm |                   |

| 32GB       | KLMBG4GE4A-A001 | 64Gb MLC x 4    | 91.0%            | (1.70V ~ 1.95V or<br>2.7V ~ 3.6V)      |                     | 169FBGA           |

| 64GB       | KLMCG8GE4A-A001 | 64Gb MLC x 8    |                  | - Memory power : VDDF<br>(2.7V ~ 3.6V) | 12mm x 16mm x 1.2mm |                   |

## 2.0 KEY FEATURES

• MultiMediaCard System Specification Ver. 4.41 compatible. Detail description is referenced by JEDEC Standard

• SAMSUNG e·MMC supports below special features which are being discussed in JEDEC

- High Priority Interrupt scheme is supported

- Back ground operation is supported.

- Full backward compatibility with previous MultiMediaCard system (1bit data bus, multi-e·MMC systems)

- Data bus width : 1bit (Default), 4bit and 8bit

- MMC I/F Clock Frequency : 0 ~ 52MHz MMC I/F Boot Frequency : 0 ~ 52MHz

- Temperature : Operation(-25°C ~ 85°C), Storage without operation (-40°C ~ 85°C)

- Power : Interface power  $\rightarrow$  VDD (1.70V ~ 1.95V or 2.7V ~ 3.6V) , Memory power  $\rightarrow$  VDDF(2.7V ~ 3.6V)

## datasheet

## **3.0 PACKAGE CONFIGURATIONS**

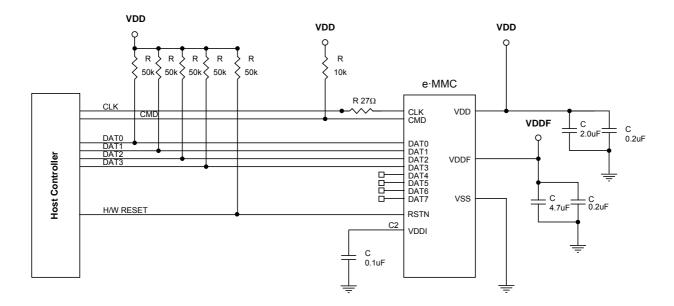

## 3.1 169 Ball Pin Configuration

#### [Table 2] 169 Ball Information

| Pin NO | Name | Pin NO | Name |    |

|--------|------|--------|------|----|

| K6     | VDD  | AA5    | VDD  |    |

| T10    | VDDF | W4     | VDD  | DN |

| K2     | VDDI | Y4     | VDD  | DM |

| R10    | Vss  | AA3    | VDD  | 10 |

| W5     | CMD  | U9     | VDDF | 10 |

| W6     | CLK  | M6     | VDDF |    |

| H3     | DAT0 | N5     | VDDF |    |

| H4     | DAT1 | U8     | Vss  |    |

| H5     | DAT2 | M7     | Vss  |    |

| J2     | DAT3 | AA6    | Vss  |    |

| J3     | DAT4 | P5     | Vss  |    |

| J4     | DAT5 | Y5     | Vss  |    |

| J5     | DAT6 | K4     | Vss  |    |

| J6     | DAT7 | Y2     | Vss  |    |

| H6     | RFU  | AA4    | Vss  |    |

| H7     | RFU  | U5     | RSTN |    |

| K5     | RFU  |        |      |    |

| M5     | RFU  |        |      |    |

| M8     | RFU  |        |      |    |

| M9     | RFU  |        |      |    |

| M10    | RFU  |        |      |    |

| N10    | RFU  |        |      |    |

| P3     | RFU  |        |      |    |

| P10    | RFU  |        |      |    |

| R5     | RFU  |        |      |    |

| T5     | RFU  |        |      |    |

| U6     | RFU  |        |      | D  |

| U7     | RFU  |        |      | D  |

| U10    | RFU  |        |      | זס |

| AA7    | RFU  |        |      |    |

| AA10   | RFU  |        |      |    |

Figure 1. 169-FBGA

#A1 INDEX MARK

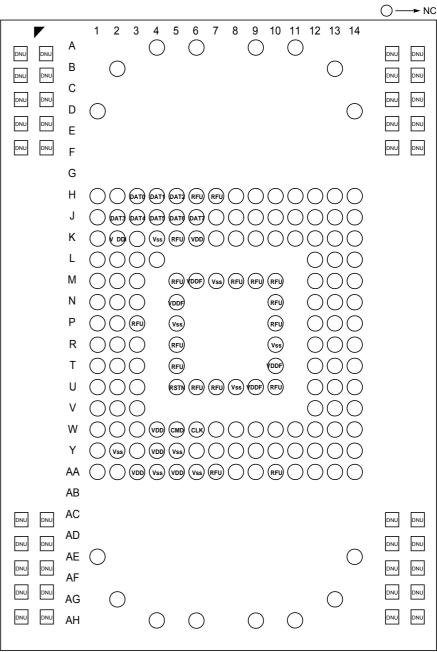

### 3.1.1 12mm x 16mm x 1.0mm Package Dimension

Figure 2. 12mm x 16mm x 1.0mm Package Dimension

#A1 INDEX MARK

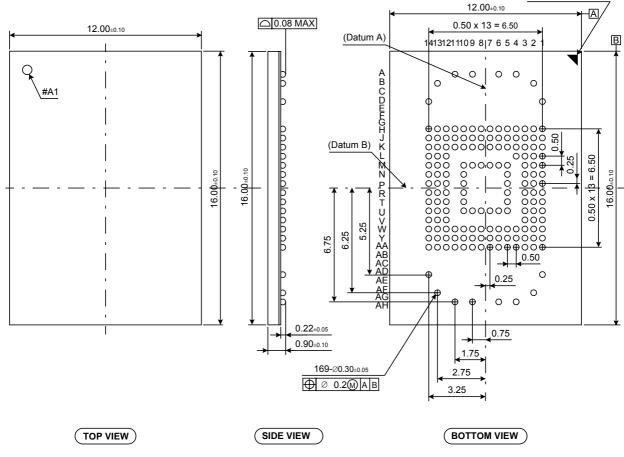

### 3.1.2 12mm x 16mm x 1.2mm Package Dimension

Figure 3. 12mm x 16mm x 1.2mm Package Dimension

### 3.2 Product Architecture

- e·MMC consists of NAND Flash and Controller. VDD is for Controller power and VDDF is for flash power

Figure 4. e-MMC Block Diagram

datasheet

## 4.0 e.MMC 4.41 features

## 4.1 Data Write

Host can configure reliability mode to protect existing data per each partition.

This relibility mode has to be set before partitioning is completed.

This reliability setting only impacts the reliability of the main user area and the general purpose partitions.

#### [Table 3] EXT\_CSD value for reliability setting in write operation

| Name                           | Field        | Size<br>(Bytes) | Cell Type | EXT_CSD-slice | Value |

|--------------------------------|--------------|-----------------|-----------|---------------|-------|

| Data Reliability Supports      | WR_REL_PARAM | 1               | R         | 166           | 0x05  |

| Data Reliability Configuration | WR_REL_SET   | 1               | R/W       | 167           | 0x1F  |

#### Explanation of each field in the upper table is mentioned below

#### [Table 4] Definition of EXT\_CSD value for reliability setting

| Fields      | Definitions                                                                                                                                                     |

|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HS_CTRL_REL | 0x0: All the WR_DATA_REL parameters in the WR_REL_SET registers are read only bits.<br>0x1: All the WR_DATA_REL parameters in the WR_REL_SET registers are R/W. |

| EN_REL_WR   | 0x0: The device supports the previous definition of reliable write.<br>0x1: The device supports the enhanced definition of reliable write                       |

#### The below table shows each field for WE\_REL\_SET

#### [Table 5] Description of each field for WE\_REL\_SET

| Name                               | Field           | Bit | Size | Туре                                           |

|------------------------------------|-----------------|-----|------|------------------------------------------------|

| Write Data Reliability (user Area) | WR_DATA_REL_USR | 0   | 1    | R (if HS_CTRL_REL=0)<br>R/W (if HS_CTRL_REL=1) |

| Write Data Reliability Partition 1 | WR_DATA_REL_1   | 1   | 1    | R (if HS_CTRL_REL=0)<br>R/W (if HS_CTRL_REL=1) |

| Write Data Reliability Partition 2 | WR_DATA_REL_2   | 2   | 1    | R (if HS_CTRL_REL=0)<br>R/W (if HS_CTRL_REL=1) |

| Write Data Reliability Partition 3 | WR_DATA_REL_3   | 3   | 1    | R (if HS_CTRL_REL=0)<br>R/W (if HS_CTRL_REL=1) |

| Write Data Reliability Partition 4 | WR_DATA_REL_4   | 4   | 1    | R (if HS_CTRL_REL=0)<br>R/W (if HS_CTRL_REL=1) |

| Reserved                           | -               | 7:5 | -    | -                                              |

## 4.2 Reliable Write

[Table 6] EXT\_CSD value for reliable write

| Name                      | Field        | Size (Bytes) | Cell Type | CSD-slice | Value |

|---------------------------|--------------|--------------|-----------|-----------|-------|

| Data Reliability Supports | WR_REL_PARAM | 1            | R         | 166       | 0x05  |

Reliable write with EN\_REL\_WR is 0x1 supports atomicity of sector unit.

The block size defined by SET\_BLOCKLEN (CMD16) is ignored and reliable write is executed as only 512 byte length. There is no imit on the size of the reliable write.

[Table 7] EXT\_CSD value for reliable write

| Name                        | Field        | Size<br>(Bytes) | Cell Type | CSD-slice | Value |

|-----------------------------|--------------|-----------------|-----------|-----------|-------|

| Reliable Write Sector Count | REL_WR_SEC_C | 1               | R         | [222]     | 0x01  |

#### 4.3 Secure Trim

Secure Trim operation consists of Secure Trim Step1 and Secure Trim Step2.

In Secure Trim Step 1 the host defines the range of write blocks that it would like to mark for the secure purge.

[Table 8] EXT\_CSD value for secure trim

| Field         | Definitions                                                            | Value |

|---------------|------------------------------------------------------------------------|-------|

| SEC_TRIM_MULT | Secure Trim Step2 Timeout = 300ms x ERASE_TIMEOUT_MULT x SEC_TRIM_MULT | 0x11  |

Area marked by Secure Trim Step1 is shown as EXT\_CSD[181](ERASED\_MEM\_CONT) before Secure Trim Step2 is completed.

When Secure Trim Step2 is issued, if there is no data marked by Secure Trim Step1, Secure Trim Step2 does not work.

## 4.4 High Priority Interrupt

High Priority Interrupt is to stop ongoing operation and perform read operation with high priority

Command set for High Priority Interrupt operation is the below

[Table 9] Command List for High Priority Interrupt

| CMD Index | Туре | Argument                                                                                                                          | Resp | Abbreviation | Command Description                                                                                                |

|-----------|------|-----------------------------------------------------------------------------------------------------------------------------------|------|--------------|--------------------------------------------------------------------------------------------------------------------|

| CMD12     | ас   | [31:16] – RCA*<br>[15:1] – stuff bits<br>[0] – High Priority Interrupt *<br>*To be used only to send a High<br>Priority Interrupt | R1b  |              | If High Priority Interrupt flag is set the device shall interrupt its internal operations in a well defined timing |

Interruptible commands by read while write operation are the below.

#### [Table 10] List of Interruptible Command

| Commands | Names                 | Notes                                                                                                                         |

|----------|-----------------------|-------------------------------------------------------------------------------------------------------------------------------|

| CMD24    | WRITE SINGLE BLOCK    | -                                                                                                                             |

| CMD25    | WRITE MULTIPLE BLOCKS | -                                                                                                                             |

| CMD25    | RELIABLE WRITE        | Stopping a reliable write command<br>with 'High Priority Interrupt' flag set turns that command into a reliable write command |

|          | ERASE                 | -                                                                                                                             |

| CMD38    | TRIM                  | -                                                                                                                             |

| CINIDGO  | SECURE ERASE          | -                                                                                                                             |

|          | SECURE TRIM           | -                                                                                                                             |

| CMD6     | SWITCH                | BACKGROUND OPERATION ONLY                                                                                                     |

### KLMxGxGE4A-A001

# datasheet

#### [Table 11] EXT\_CSD value for HPI

| Name                                   | Field                     | Size(Bytes) | Cell Type | CSD-Slice | Value |

|----------------------------------------|---------------------------|-------------|-----------|-----------|-------|

| HPI features                           | HPI_FEATURES              | 1           | R         | [503]     | 0x03  |

| Number of correctiy programmed sectors | CORRECTLY_PRG_SECTORS_NUM | 4           | R         | [245:242] | 0x00  |

| Partition switching timing             | PARTITION_SWITCH_TIME     | 1           | R         | [199]     | 0x01  |

| Out of interrupt busytiming            | OUT_OF_INTERRUPT_TIME     | 1           | R         | [198]     | 0x02  |

| HPI management                         | HPI_MGMT                  | 1           | R/W/E_P   | [161]     | 0x00  |

#### [Table 12] Definition of EXT\_CSD value for HPI

| Fields                   | Definitions                                                                                                                                                                                                                                                                                       |

|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPI_FEATURES             | Bit 0 means HPI_SUPPORT<br>Bit 0 = 0x0 : High Priority Interrupt mechanism not supported<br>Bit 0 = 0x1 : High Priority Interrupt mechanism supported<br>Bit 1 means HPI_IMPLEMENTATION<br>0x0 : HPI mechanism implementation based on CMD13<br>0x1 : HPI mechanism implementation based on CMD12 |

| CORRECTLY_PRG_SECTOR_NUM | This field indicates how many 512B sectors were successfully programmed by the last<br>WRITE_MULTIPLE_BLOCK command (CMD25).<br>CORRECTLY_PRG_SECTORS_NUM=EXT_CSD[242]*2^0+EXT_CSD[243]*2^8<br>+EXT_CSD[244]*2^16 + EXT_CSD[245]*2^24                                                             |

| PARTITION_SWITCH_TIME    | This field indicates the maximum timeout for the SWITCH command (CMD6) when switching partitions by changing PARTITION_ACCESS bits in PARTITION_CONFIG field (EXT_CSD byte [179]). Time is expressed in units of 10 milliseconds                                                                  |

| OUT_OF_INTERRUPT_TIME    | This field indicates the maximum timeout to close a command interrupted by HPI - time between the end bit of CMD12 / CMD 13 to the DAT0 release by the device.                                                                                                                                    |

| HPI_MGMT                 | Bit 0 means HPI_EN<br>0x0 : HPI mechanism not activated by the host<br>0x1 : HPI mechanism activated by the host                                                                                                                                                                                  |

# datasheet

## 4.5 Background Operation

When the host is not being serviced, e-MMC can do internal operation by using "Background Operation" command. In this operation which takes long time to complete can be handled later when host ensure enough idle time (In Back ground operation)

Background Operation Sequence is the following

#### [Table 13] Background Operation Sequence

| Function                   | Command                      | Description                                                                                                                                                        |

|----------------------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Background Operation Check | CMD8 Or Card Status Register | If BKOPS_STATUS is not 0 or $d^h$ bit of card status register is set, there are something to be performed by background operation                                  |

| Background Operation Start | CMD6                         | Background operation starts by BKOPS_START is set to any value.<br>When background operation is completed BKOPS_STATUS is set to 0<br>and BKOPS_START is set to 0. |

| Background Operation Stop  | HPI                          | If the background operation is stopped<br>BKOPS_START is set to 0                                                                                                  |

#### [Table 14] EXT\_CSD value for Background Operation

| Name                                    | Field         | Size(Bytes) | Cell Type | CSD-Slice | Value |

|-----------------------------------------|---------------|-------------|-----------|-----------|-------|

| Background operations Support           | BKOPS_SUPPORT | 1           | R         | [502]     | 0x01  |

| Background operations status            | BKOPS_STATUS  | 1           | R         | [246]     | 0x00  |

| Manually start background operations    | BKOPS_START   | 1           | W/E_P     | [164]     | 0x00  |

| Enable background operations hand shake | BKOP_EN       | 1           | R/W       | [163]     | 0x00  |

#### [Table 15] Definition of EXT\_CSD value for Bakgrourd Operation

| Fields        | Definitions                                                                                                                                                                                                                                                            |

|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BKOPS_SUPPORT | <ul><li>'0' means Background operation is not supported</li><li>'1' means Background operation is supported</li></ul>                                                                                                                                                  |

| BKOPS_ STATUS | <ul> <li>'0' means No background work pending</li> <li>'1' means pending background work existing.</li> <li>'2' means pending background work existing &amp; performance being impacted.</li> <li>'3' means pending background work existing &amp; critical</li> </ul> |

| BKOPS_START   | Background operation start while BKOPS_START is set to any value.<br>'0' means Background operation is enabled.                                                                                                                                                        |

| BKOPS_EN      | <ul><li>'0' means host does not support background operation</li><li>'1' means host use background operation manually</li></ul>                                                                                                                                        |

#### [Table 16] Card Status Register for Background Operation

| Bits | Identifier   | Туре | Det Mode | Value | Description                                                                                                                                                                       | Clear Cond |

|------|--------------|------|----------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 6    | URGENT_BKOPS | S    | R        |       | If set, device needs to perform background opera-<br>tions urgently. Host can check EXT_CSD field<br>BKOPS_STATUS for the detailed level<br>( in case of BKOPS_STATUS is 2 or 3 ) | А          |

## 5.0 Technical Notes

### 5.1 S/W Agorithm

#### 5.1.1 Partition Management

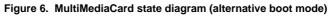

The device initially consists of two Boot Partitions and RPMB Partition and User Data Area.

The User Data Area can be divided into four General Purpose Area Partitions and User Data Area partition. Each of the General Purpose Area partitions and a section of User Data Area partition can be configured as enhanced partition.

#### 5.1.1.1 Boot Area Partition and RPMB Area Partition

Default size of each Boot Area Partition is 512KB and can be changed by Vendor Command as multiple of 512KB. Default size of RPMB Area Partition is 128 KB and can be changed by Vendor Command as multiple of 128KB.

Boot Partition size & RPMB Partition Size are set by the following command sequence :

| Table 17 | 1 Sotting coguoned | of Root Aroa Dartition | n size and RPMB Area Partition size  |   |

|----------|--------------------|------------------------|--------------------------------------|---|

|          | I Setting Sequence |                        | I SIZE ANU KEIVID AIEA FAILILUI SIZE | ; |

|          |                    |                        |                                      |   |

| Function                   | Command                | Description                                                             |

|----------------------------|------------------------|-------------------------------------------------------------------------|

| Partition Size Change Mode | CMD62(0xEFAC62EC)      | Enter the Partition Size Change Mode                                    |

| Partition Size Set Mode    | CMD62(0x00CBAEA7)      | Partition Size setting mode                                             |

| Set Boot Partition Size    | CMD62(BOOT_SIZE_MULTI) | Boot Partition Size value                                               |

| Set RPMB Partition Size    | CMD62(RPMB_SIZE_MULTI) | RPMB Partition Size value<br>F/W Re-Partition is executed in this step. |

| Power Cycle                |                        |                                                                         |

Boot partition size is calculated as ( 128KB \* BOOT\_SIZE\_MULTI ) BOOT\_SIZE\_MULTI should be set as multiple of 8.

The size of Boot Area Partition 1 and 2 can not be set independently. It is set as same value.

RPMB partition size is calculated as ( 128KB \* RPMB\_SIZE\_MULTI ). In RPMB partition, CMD 0, 6, 8, 12, 13, 15, 18, 23, 25 are admitted.

Access Size of RPMB partition is defined as the below:

[Table 18] REL\_WR\_SEC\_C value for write operation on RPMB partition

| REL_WR_SEC_C     | Description                                                                              |

|------------------|------------------------------------------------------------------------------------------|

| REL_WR_SEC_C = 1 | Access sizes 256B and 512B supported to RPMB partition                                   |

| REL_WR_SEC_C > 1 | Access sizes up to REL_WR_SEC_C * 512B supported to RPMB partition with 256B granularity |

Any undefined set of parameters or sequence of commands results in failure access.

If the failure is in data programming case, the data is not programmed. And if the failure occurs in data read case, the read data is '0x00'.

#### 5.1.1.2 Enhanced Partition (Area)

SAMSUNG e·MMC adopts Enhanced User Data Area as SLC Mode. Therefore when master adopts some portion as enhanced user data area in User Data Area, that area occupies double size of original set up size. (ex> if master set 1MB for enhanced mode, total 2MB user data area is needed to generate 1MB enhanced area)

Max Enhanced User Data Area size is defined as (MAX\_ENH\_SIZE\_MULT x HC\_WP\_GRP\_SIZE x HC\_ERASE\_GPR\_SIZE x 512kBytes)

#### 5.1.2 Write protect management

In order to allow the host to protect data against erase or write, the device shall support write protect commands.

#### 5.1.2.1 User Area Write Protection

TMP\_WRITE\_PROTECT (CSD[12]) and PERM\_WRITE\_PROTECT(CSD[13]) registers allow the host to apply write protection to whole device including Boot Partition, RPMB Partition and User Area.

#### [Table 19] whole device write protect priority

| Class                   | Setting                     |

|-------------------------|-----------------------------|

| Permanent write protect | SET : One time programmable |

| r emanent while protect | CLR : Not available         |

| Temporary write protect | SET : Multiple programmable |

| remporary write protect | CLR : Multiple programmable |

USER\_WP (EXT\_CSD[171]) register allows the host to apply write protection to all the partitions in the user area.

#### [Table 20] User area write protect priority

| Class                   | Setting                                 |

|-------------------------|-----------------------------------------|

| Permanent write protect | SET : One time programmable             |

| r emanent while protect | CLR : Not available                     |

| Power-on write protect  | SET : One time programmable on power-on |

|                         | CLR : After power reset                 |

| Temporary write protect | SET : Multiple programmable             |

|                         | CLR : Multiple programmable             |

The host has the ability to check the write protection status of segments by using the SEND\_WRITE\_PROT\_TYPE command (CMD31). Wh en full card protection is enabled all the segments will be shown as having permanent protection.

#### 5.1.2.2 Boot Partition Write Protection

BOOT\_WP (EXT\_CSD [173]) register allows the host to apply write protection to Boot Area Partitions.

[Table 21] Boot area write protect priority

| Class                    | Setting                                 |

|--------------------------|-----------------------------------------|

| Permanent write protect  | SET : One time programmable             |

| r enhanent white protect | CLR : Not available                     |

| Power-on write protect   | SET : One time programmable on power-on |

| r ower-on white protect  | CLR : After power reset                 |

An attempt to set both the disable and enable bit for a given protection mode (permanent or power-on) in a single switch comman d will have no impact and switch error occurs.

Setting both B\_PERM\_WP\_EN and B\_PWR\_WP\_EN will result in the boot area being permanently protected.

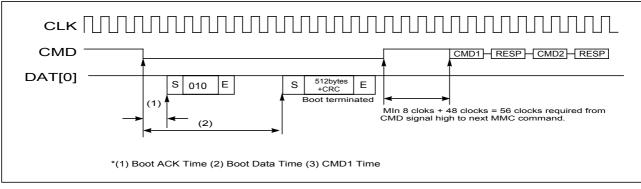

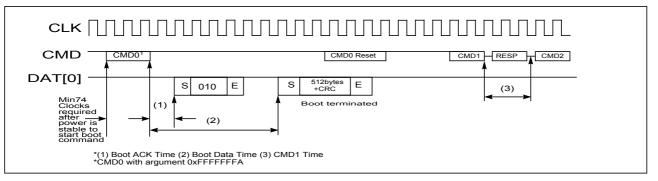

#### 5.1.3 Boot operation

Device supports not only boot mode but also alternative boot mode. Device supports high speed timing and dual data rate during boot

#### [Table 22] Boot ack, boot data and initialization Time

| Timing Factor                         | Value    |

|---------------------------------------|----------|

| (1) Boot ACK Time                     | < 50 ms  |

| (2) Boot Data Time                    | < 60 ms  |

| (3) Initialization Time <sup>1)</sup> | < 3 secs |

NOTE:

1) This initialization time includes partition setting, Please refer to INI\_TIMEOUT\_AP in 6.4 Extended CSD Register.

Normal initialization time (without partition setting) is completed within 1sec

Minimum function for reading boot data is initialized during boot time and after that full function is initialized during initialization time.

#### 5.1.4 Wear Leveling

The partitions in device have the following NAND type in case of MLC type NAND.

#### [Table 23] NAND type in each partitions

| Partitions                |               | NAND Operation Mode  |

|---------------------------|---------------|----------------------|

| Boot Area Partition 1     |               | SLC Mode             |

| Boot Area Partition 2     |               | SLC Mode             |

| RPMB Area Partition       |               | SLC Mode             |

| General Purpose Partition |               | MLC Mode or SLC Mode |

| User Data Area            | Enhanced Area | SLC Mode             |

|                           | Default Area  | MLC Mode             |

Wear leveling means that blocks should be used evenly in order to expand life span of device. Wear leveling is executed in each partition locally because of each partition with different attribute.

Figure 7. Wear leveling

And then device reserves free block and executes wear-level at each partition respectively.

#### 5.1.5 User Density

Total User Density depends on device type. For example, 32MB in the SLC Mode requires 64MB in MLC. This results in decreasing of user density

| Вс | oot Partition #1 &#</th><th>2 RPMB</th><th>4 Gen</th><th>eral Purpose Part</th><th>titions (GPA)</th><th>Enhance</th><th>ed User Data Area</th><th></th></tr><tr><th></th><th>0</th><th>2</th><th></th><th>3</th><th></th><th>4</th><th></th><th></th></tr><tr><th>  '</th><th>I</th><th></th><th>•</th><th>ł</th><th>Us</th><th>ser Density</th><th></th><th></th></tr></tbody></table> |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

[Table 24] Capacity according to partition

|     |      | Boot partition 1 | Boot partition 2 | RPMB    |

|-----|------|------------------|------------------|---------|

|     | Min. | 2,048KB          | 2,048KB          | 128KB   |

| MLC | Max. | 16,384KB         | 16,384KB         | 4,096KB |

[Table 25] Maximum Enhanced Partition Size

| Device | Max. Enhanced Partition Size |

|--------|------------------------------|

| 16 GB  | 7,801,405,440 Bytes          |

| 32 GB  | 15,602,810,880 Bytes         |

| 64 GB  | 31,247,564,800 Bytes         |

## datasheet

[Table 26] User Density Size

| Device | User Density Size    |

|--------|----------------------|

| 16 GB  | 15,634,268,160 Bytes |

| 32 GB  | 31,268,536,320 Bytes |

| 64 GB  | 62,537,072,640 Bytes |

#### 5.1.6 Auto Power Saving Mode

If host does not issue any command during a certain duration (1ms), after previously issued command is completed, the device en ters "Power Saving mode" to reduce power consumption.

At this time, commands arriving at the device while it is in power saving mode will be serviced in normal fashion

[Table 27] Auto Power Saving Mode enter and exit

| Mode                   | Enter Condition                                                                                                | Escape Condition           |

|------------------------|----------------------------------------------------------------------------------------------------------------|----------------------------|

| Auto Power Saving Mode | When previous operation which came from Host is completed and no command is issued dur-<br>ing a certain time. | If Host issues any command |

#### [Table 28] Auto Power Saving Mode and Sleep Mode

|                | Auto Power Saving Mode | Sleep Mode |

|----------------|------------------------|------------|

| NAND Power     | ON                     | OFF        |

| GotoSleep Time | < 1ms                  | < 1ms      |

#### 5.1.7 End of Life Management

The end of device life time is defined when there is no more available reserved block for bad block management in the device. When the device reaches to end of its life time, device shall change its state to permanent write protection state. In this case, write operation is not allowed any more but read operation are still allowed.

But, reliability of the operation can not be guaranteed after end of life

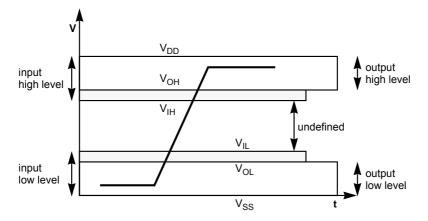

## 5.2 Smart Report